# Syntactic reasoning for digital circuits FMCAD 2016 // CSL 2017

Dan R. Ghica with Achim Jung // Aliaume Lopez // George Kaye

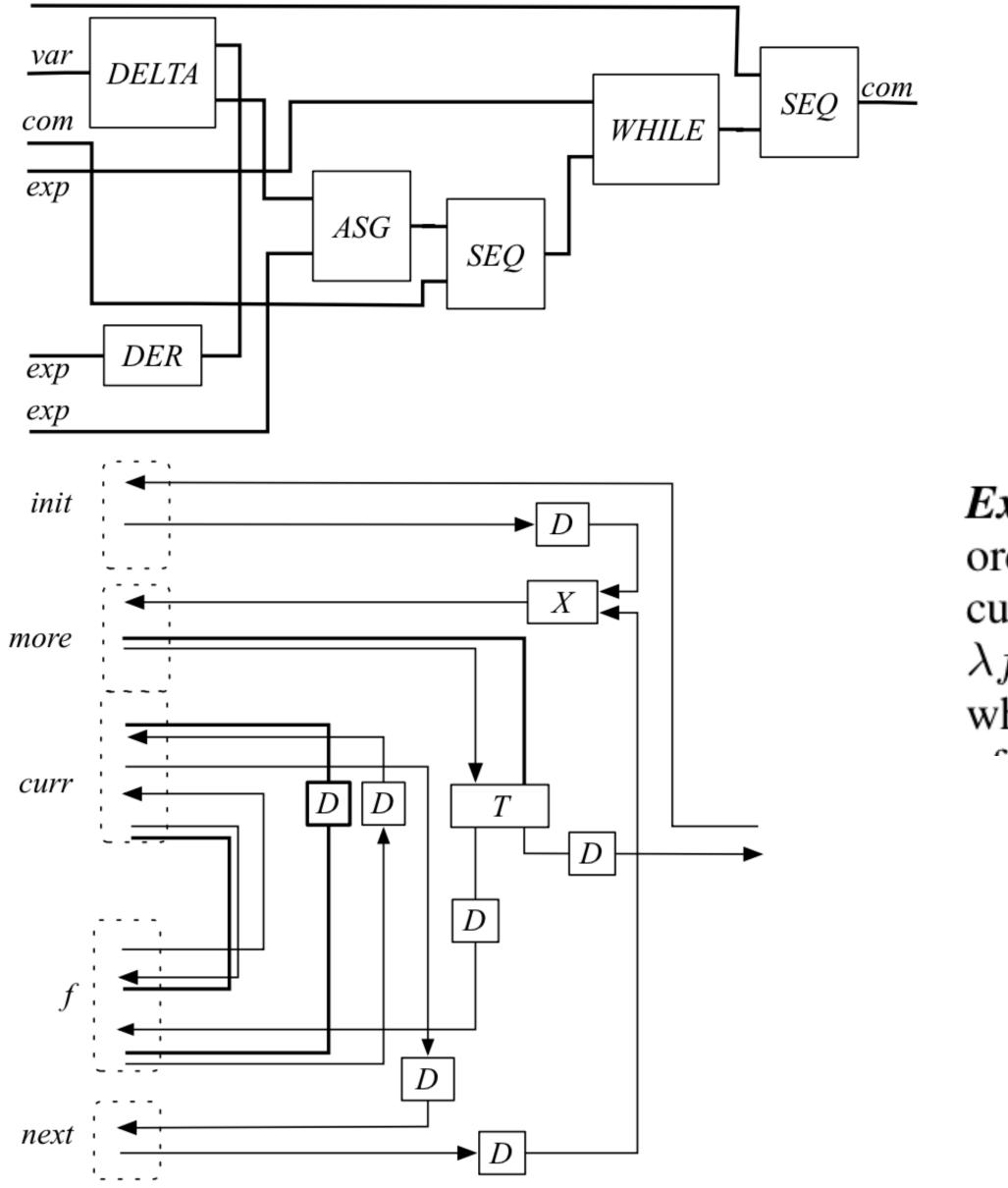

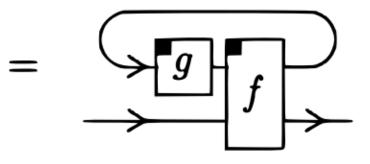

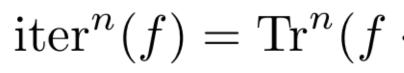

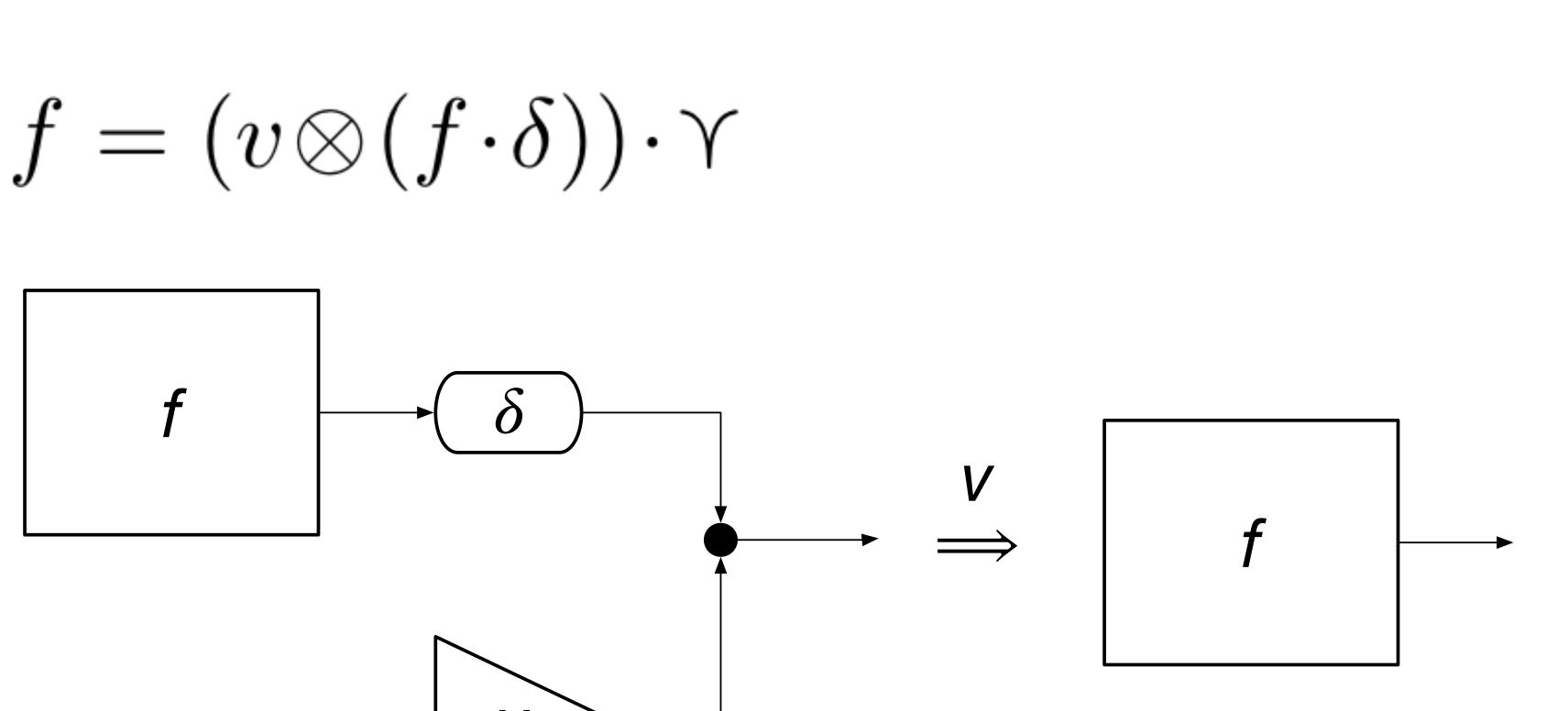

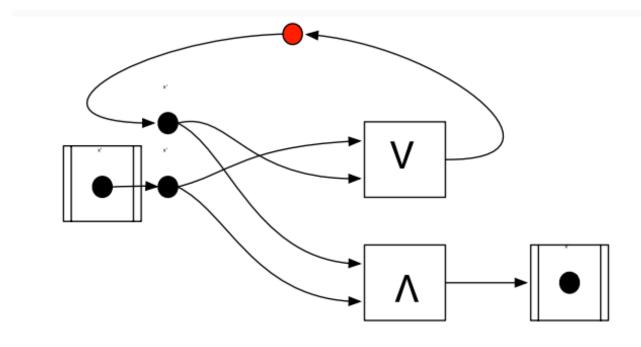

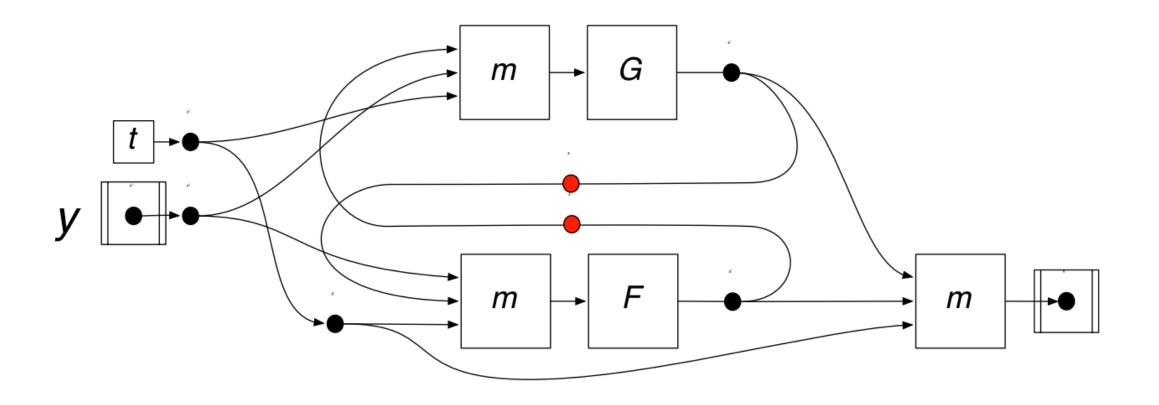

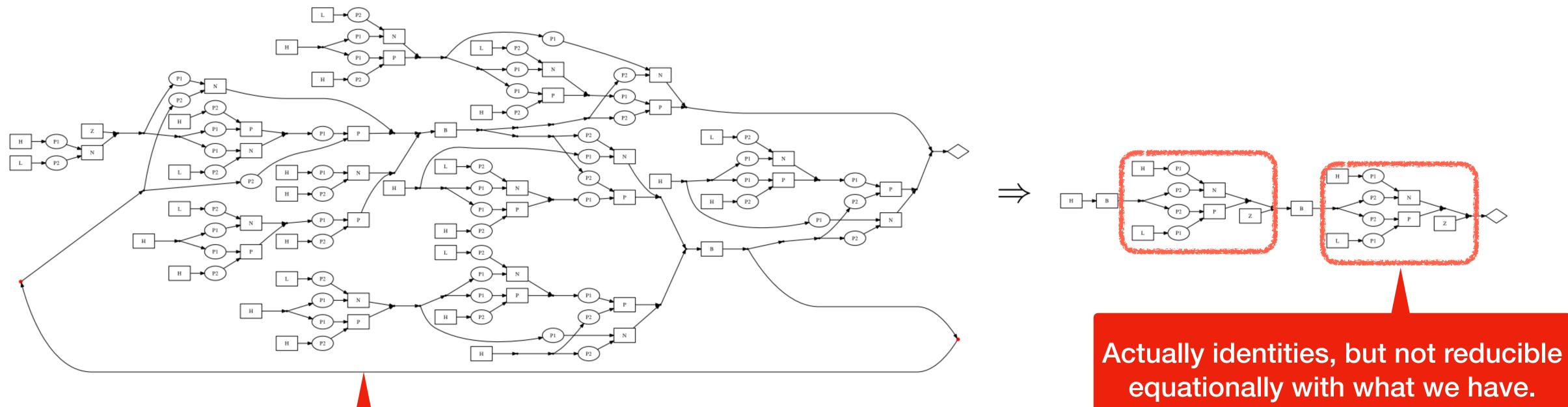

Figure 1. In-place map schematic and implementation

Dan R. Ghica, Alex I. Smith, Satnam Singh: Geometry of synthesis iv: compiling affine recursion into static hardware. ICFP 2011: 221-23

**Example.** The GoS approach allows the compilation of higherorder, open terms. Consider for example a program that executes in-place map on a data structure equipped with an iterator:  $\lambda f : \exp \rightarrow \exp.init$ ; while(more)(curr := f(!curr); next) : com, where init : com, curr : var, next : com, more : exp. The interface

**Domain-theoretic simulations are** difficult to formalise. We want syntactic reasoning (c.f. operational semantics)

Published: 28 March 2012

Michael Mendler , Thomas R. Shiple & Gérard Berry

Formal Methods in System Design 40, 283–329(2012) Cite this article 362 Accesses | 18 Citations | 0 Altmetric | Metrics

#### Constructive Boolean circuits and the exactness of timed ternary simulation

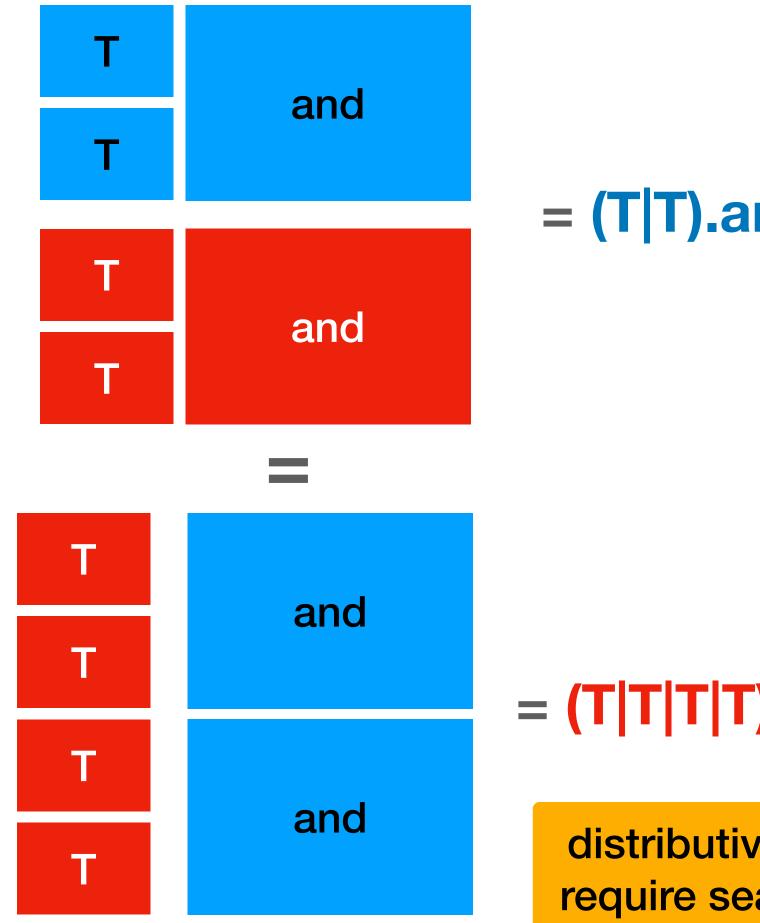

# The problem with compositional syntax or where are the redexes?

#### = (T|T).and | (T|T).and = T | T

#### **T)** . (and and) = ???

distributive laws are bidirectional and require search strategies for the redex

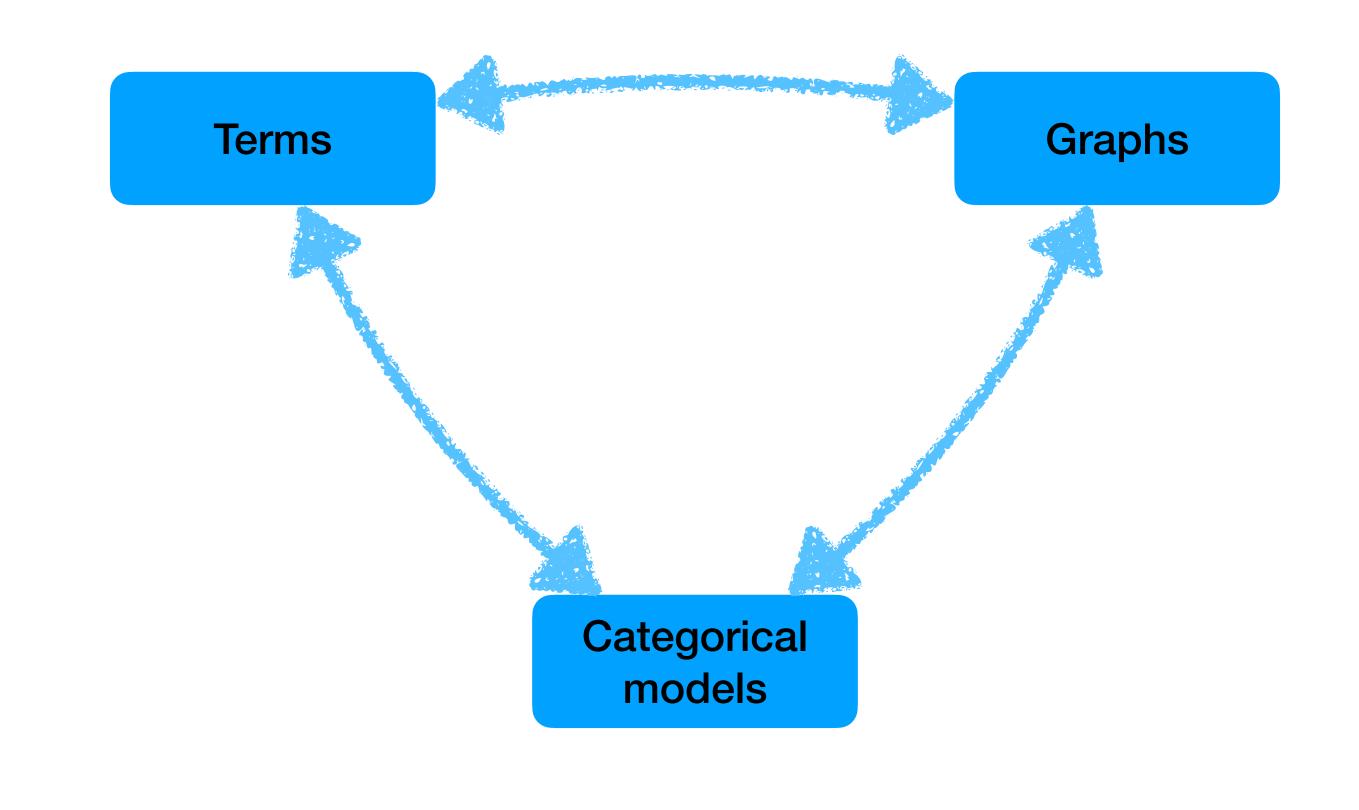

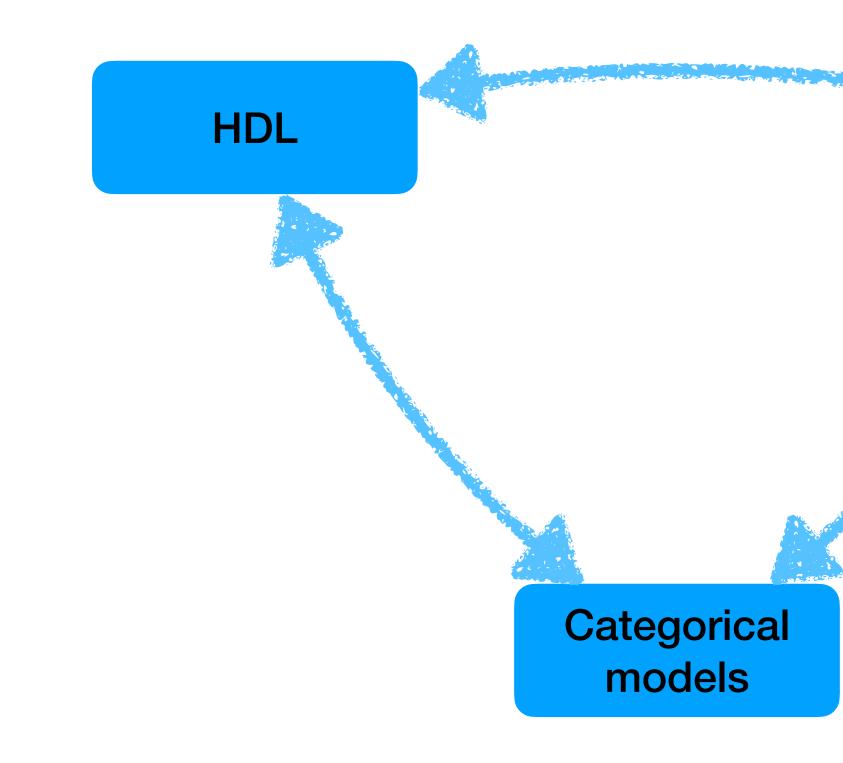

# Categorical / string diagram semantics of digital circuits

Dan R. Ghica, Achim Jung, Aliaume Lopez: Diagrammatic Semantics for Digital Circuits. CSL 2017: 24:1-24:16

Dan R. Ghica, Achim Jung: Categorical semantics of digital circuits. FMCAD 2016: 41-48

#### Monoidal hypergraphs

#### arXiv.org > math > arXiv:2010.06319

Mathematics > Category Theory

[Submitted on 13 Oct 2020 (v1), last revised 21 Oct 2020 (this version, v2)]

#### The Graphical Language of Symmetric Traced Monoidal Categories

George Kaye

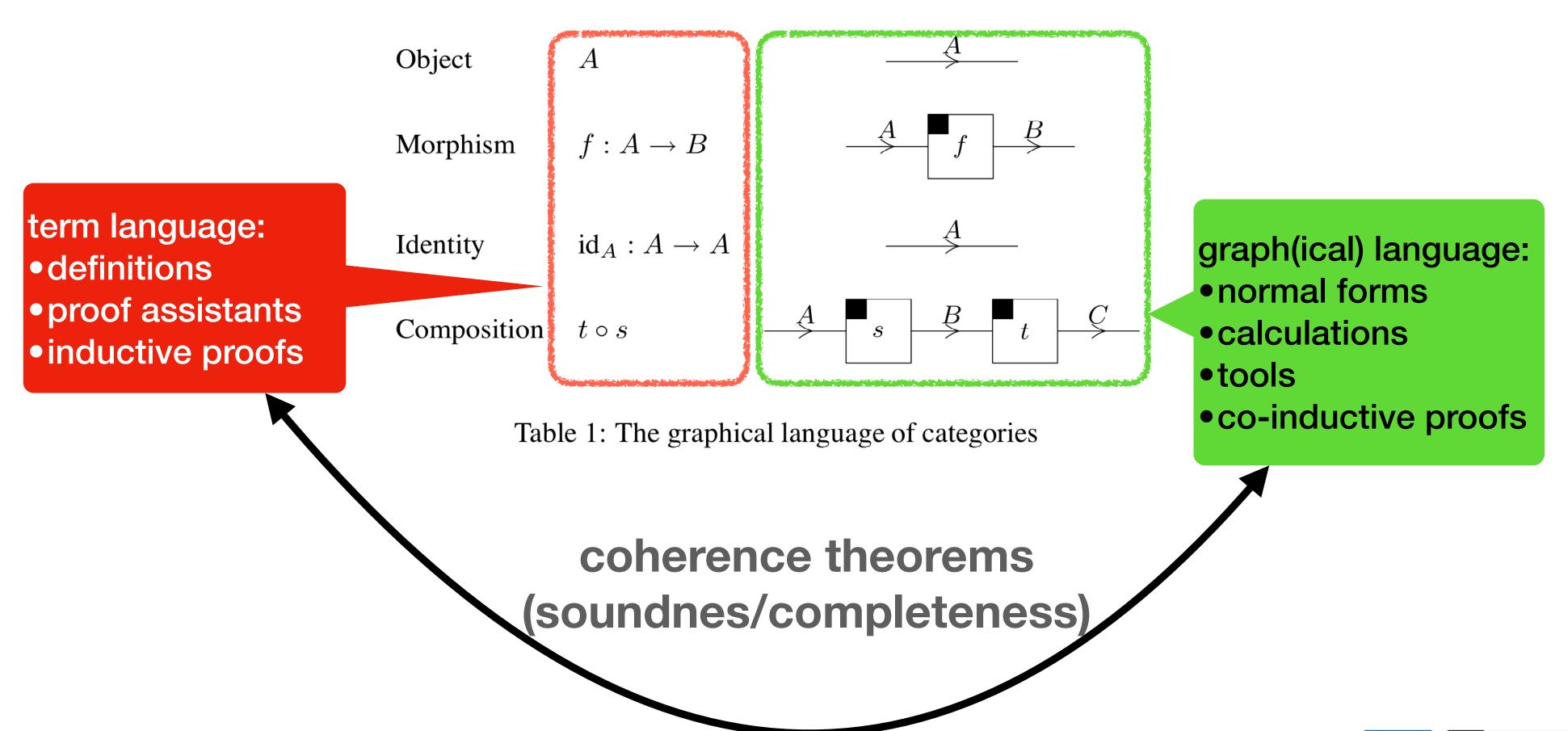

# **Solution: use graph(ical) syntax** Diagrams = graphical representations of graphs

arXiv:0908.3347 [pdf, ps, other] math.CT doi 10.1007/978-3-642-12821-9\_4 A survey of graphical languages for monoidal categories Authors: Peter Selinger

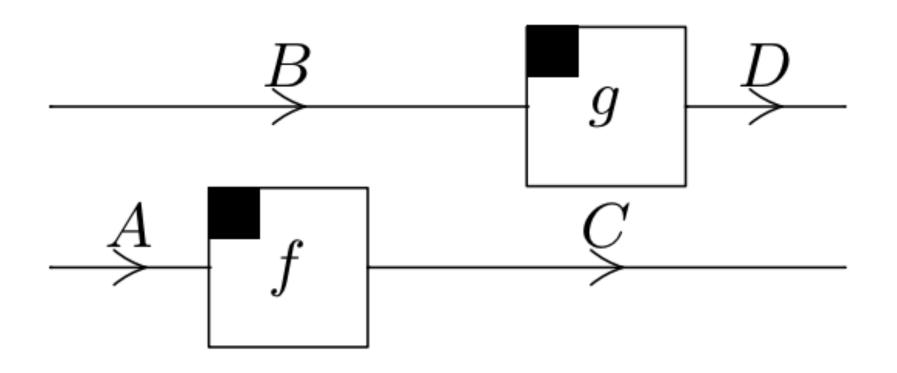

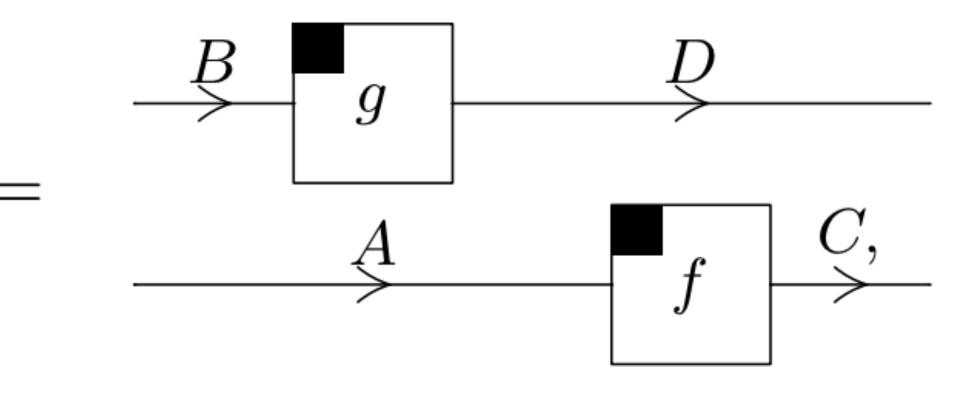

#### **Bonus!** Some equations absorbed by graph isomorphisms

- (id|f).(g|id)= (id.g) | (f.id)= g|f $= (\underline{g.id})|(id.f)$ = (g|id).(id|f)

distributivity of | ("functoriality of  $\otimes$ ") identity laws identity laws distributivity of

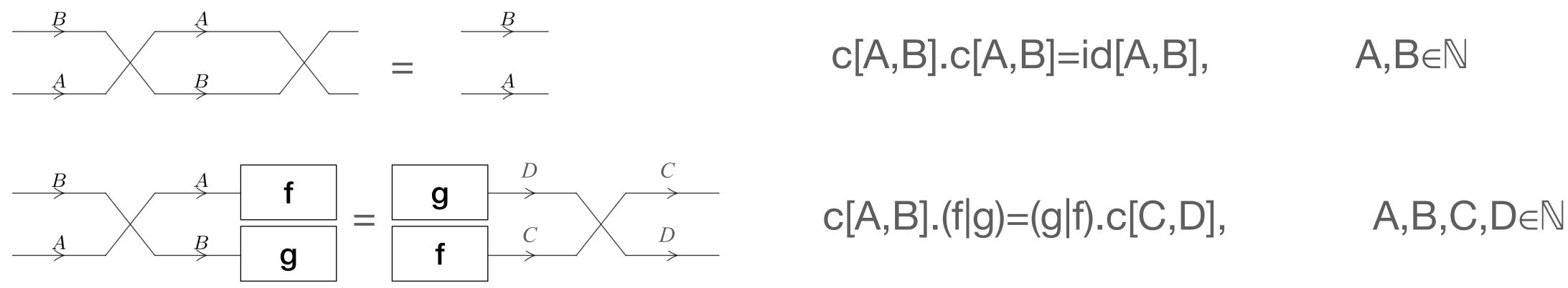

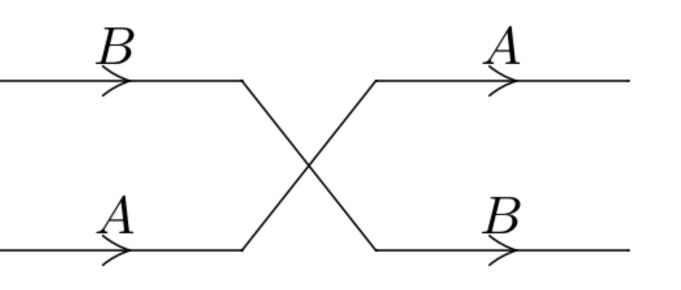

#### Symmetric monoidal category Boxes, wires, "swapping"

Symmetry  $c_{A,B}$

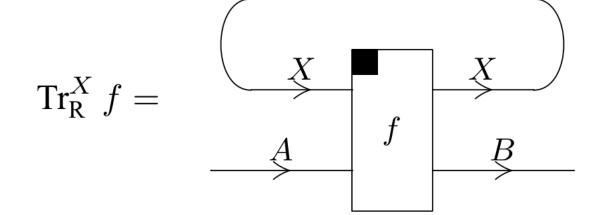

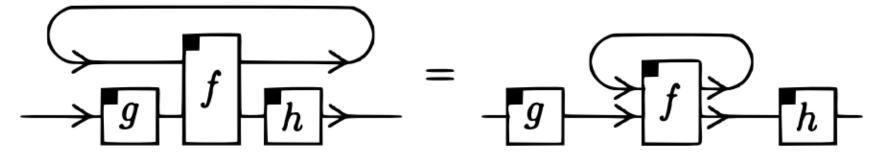

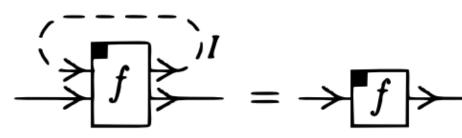

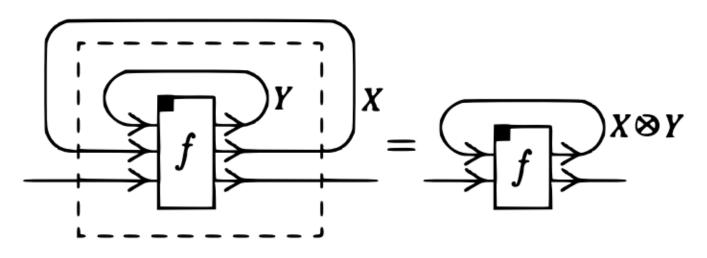

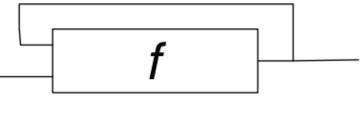

### **Feedback = "trace"** Just "hygiene" rules

Tightening:

Vanishing:

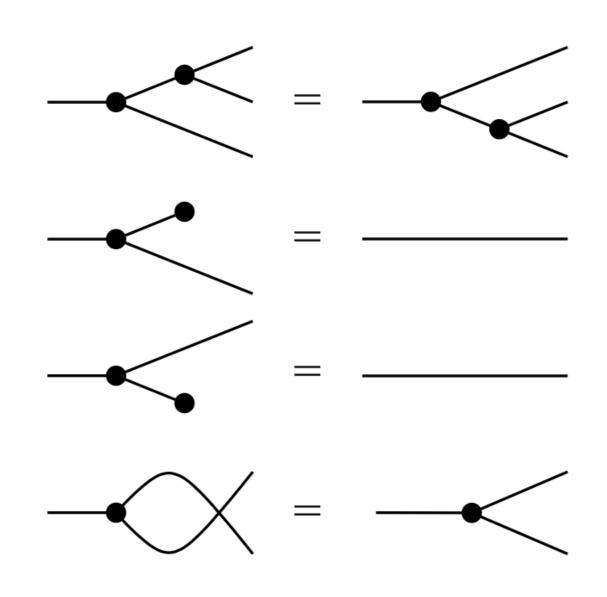

### The tensor is a product A key ingredient: copying and deletion

Commutative comonoid axioms

Table 8: Graphical representation of some product axioms

ns Naturality

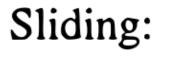

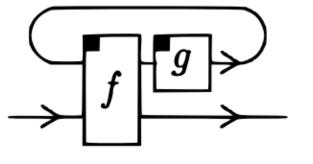

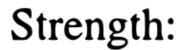

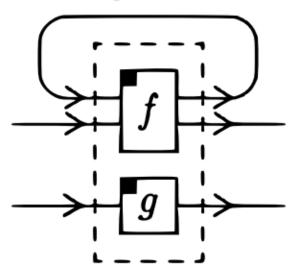

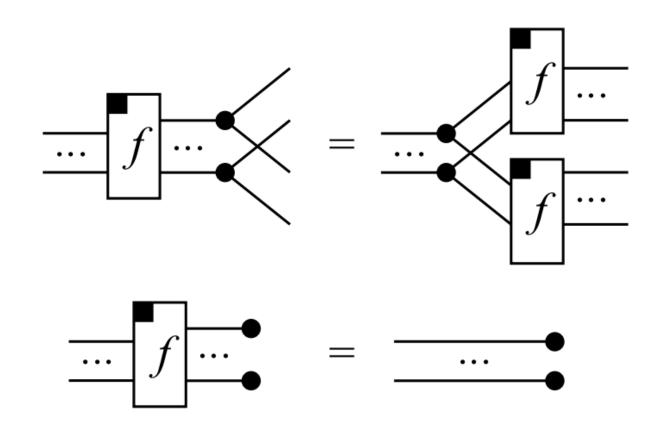

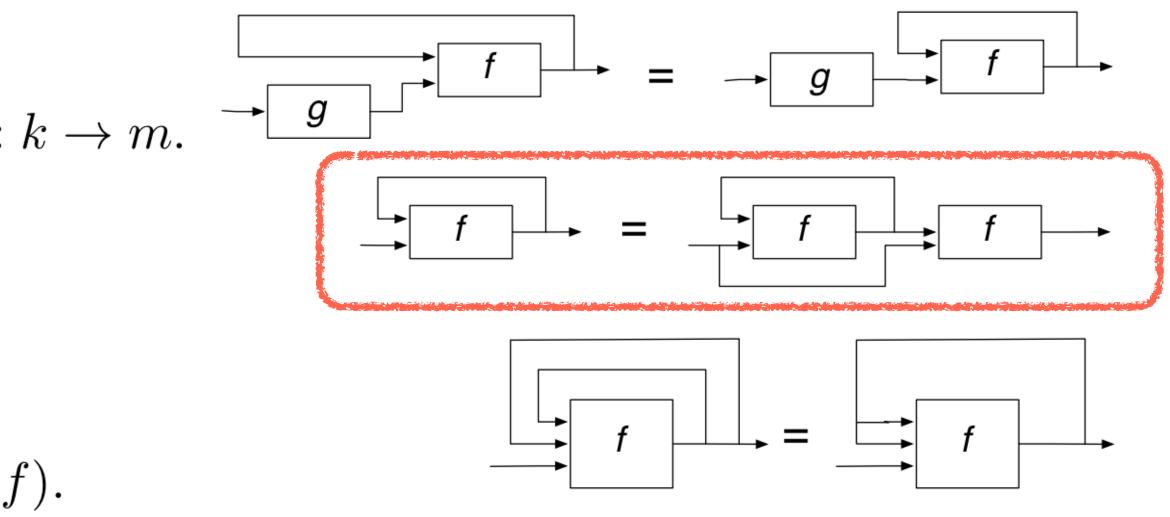

### **Trace + Product = Iteration Proper equations for feedback ("dataflow-style")**

which satisfies the following equations:

Naturality: iter $((g \otimes n) \cdot f) = g \cdot iter(f)$  for any  $g : k \to m$ .

Iteration:  $iter(f) = \langle m, iter(f) \rangle \cdot f$

Diagonal: iter<sup>n</sup>(iter<sup>n</sup>(f)) = iter<sup>n</sup>(( $\langle n, n \rangle \otimes m$ ) · f).

$\operatorname{iter}^{n}(f) = \operatorname{Tr}^{n}(f \cdot (\Delta_{n} \otimes n)) : m \to n$

Ésik. Comp. Ling. and Comp Lang'80 // Cazanescu. TCS'85 // Hasegawa. Edinburgh'97

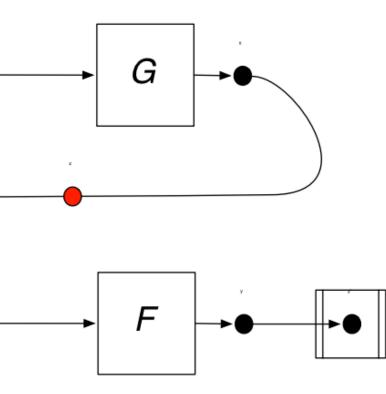

# From iteration to digital circuit models Special morphisms and axioms

- values: morphisms  $v:0 \rightarrow 1$  with a lattice structure

- gates: morphisms  $k:n \rightarrow 1$  extensional and monotonic

- join: special gate implementing join on the lattice of values

- **delays**: family of morphisms  $\delta[t]: 1 \rightarrow 1$  indexed by elements of a monoid  $t \in T$

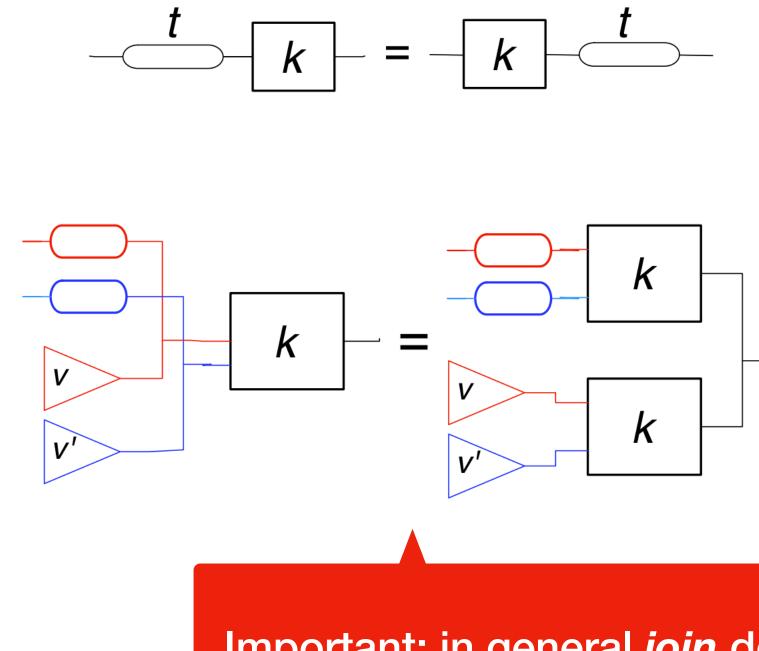

### **Special axioms Timelessness ("retiming") and Streaming**

Important: in general *join* does not induce a co-product

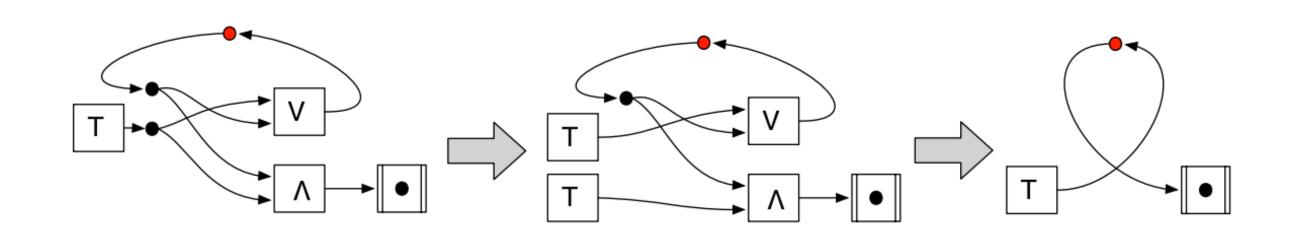

### The power of graphical reasoning **Normal forms**

Lemma 5 (Global trace). For any morphism f in a SMTC **PROP** there exists a trace-free morphisms f such that f = $\operatorname{Tr}^{A}(\hat{f})$  for some object A.

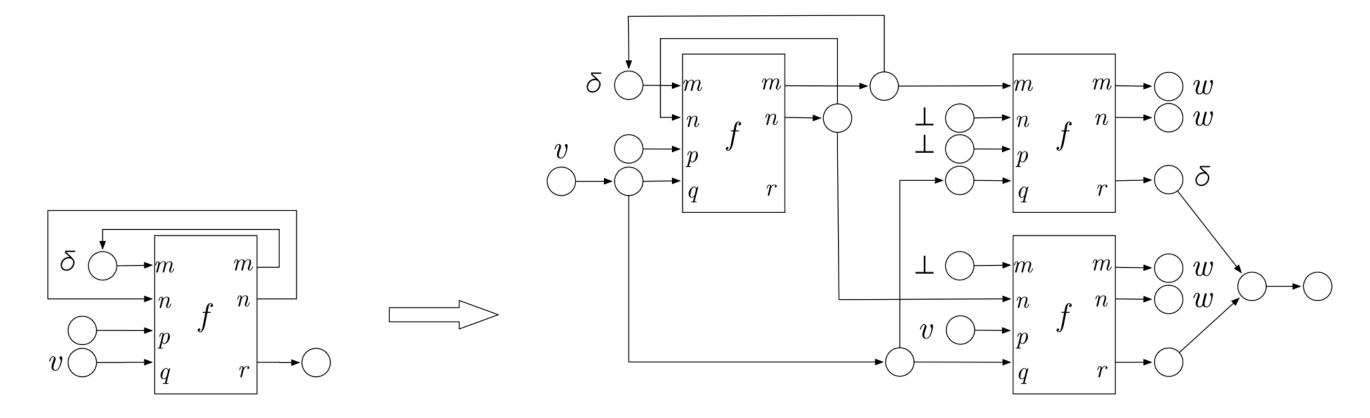

▶ Proposition 21. Given a graph representing a passified, global trace, global delay circuit,  $f: m + n + p + q \rightarrow m + n + r$ , the following rewrite rule is sound:

► Lemma 22. A passified, global-trace, global-delay circuit can be unfolded in a time linear in the size of its graph representation.

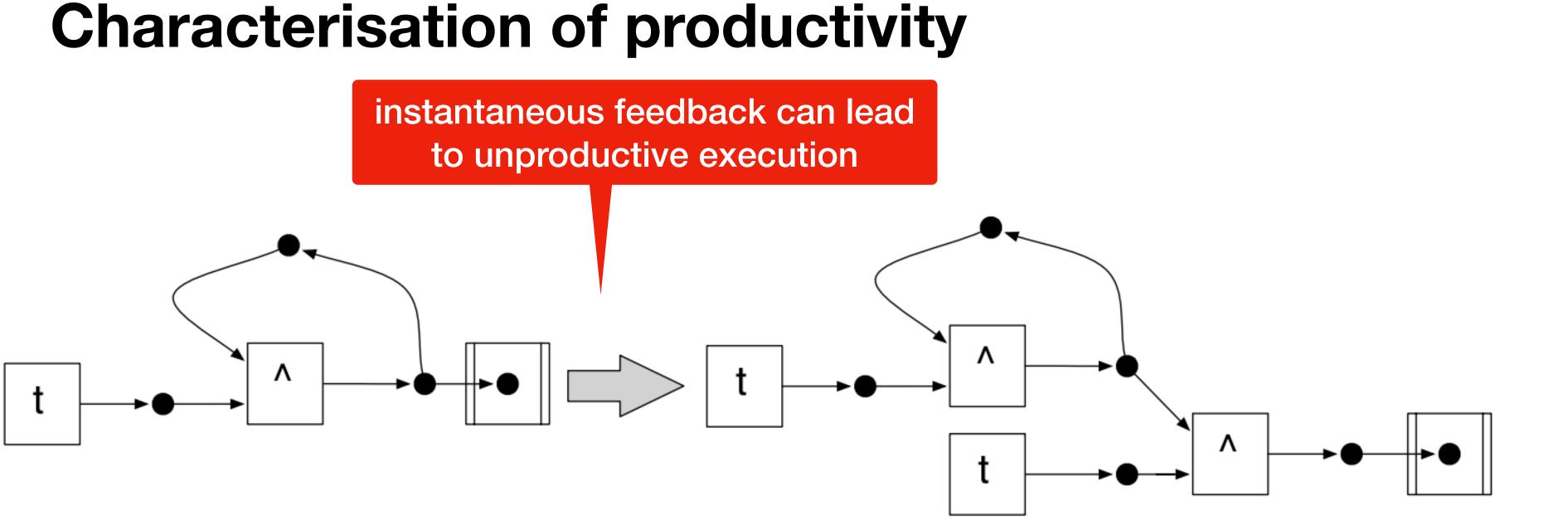

Don't get trapped unfolding unproductive local feedbacks!

Passification and global delay-form are similar to global trace. (generalisation of Mealy machines)

The proof of this key proposition is purely diagrammatic.

Efficient symbolic execution.

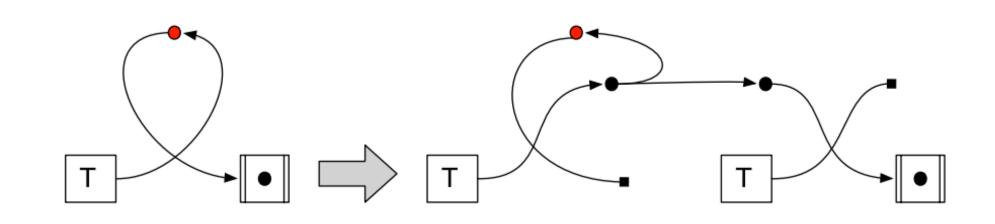

#### Key theorem (I) **Characterisation of productivity**

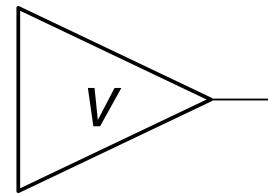

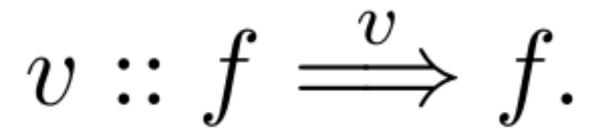

$$v :: f = (v \otimes (f \cdot \delta)) \cdot$$

# Key theorem (II) **Characterisation of productivity**

unfolding then it will always be unproductive.

► Theorem 25. If a closed, global-trace, global-delay circuit is unproductive after one

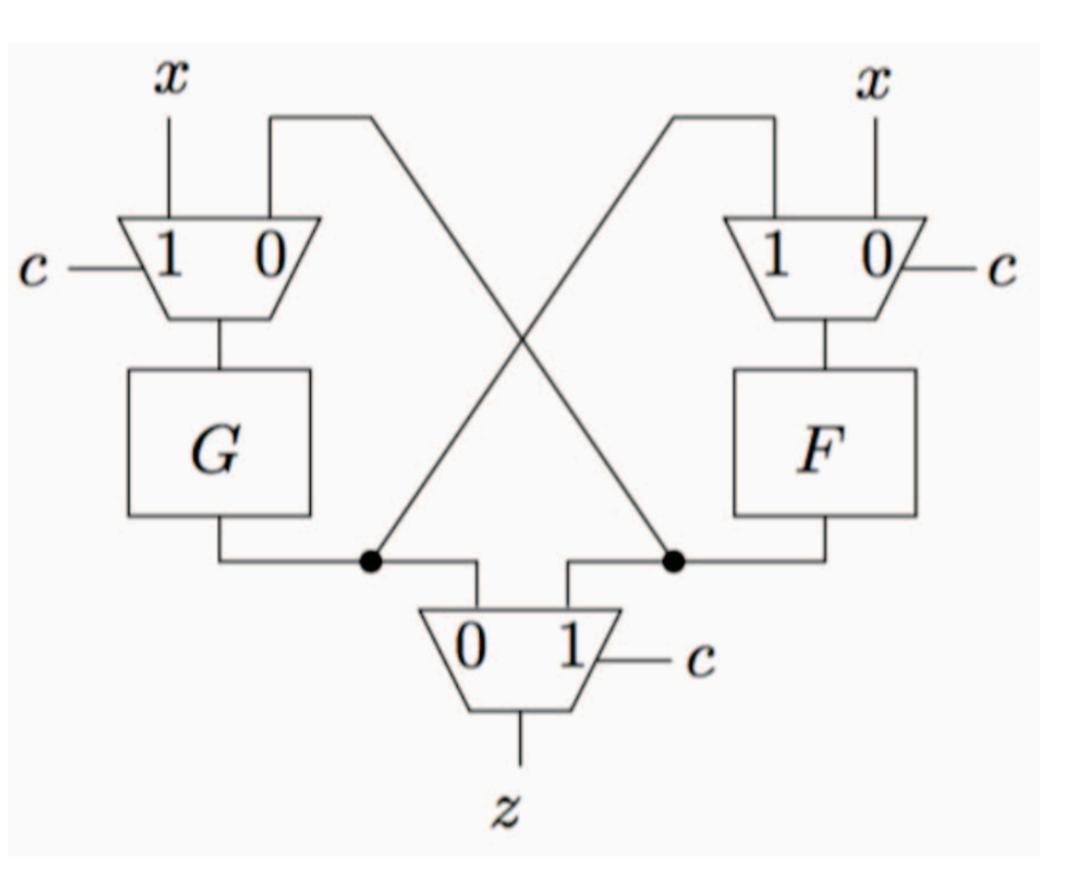

# **Example: Cyclic combinational circuits** combinational feedback // evaluation

# **Example: Cyclic combinational circuits** spurious feedback // partial evaluation

#### **Example: Pre-logical circuits Transistor-level modelling // partial evaluation**

Same circuit, implemented with pass-through CMOS logic.

# A foundational issue **Diagrammatic reasoning is sound and complete**

arXiv:2010.06319 [pdf, other] math.CT

The Graphical Language of Symmetric Traced Monoidal Categories Authors: George Kaye

**Abstract**: We examine a variant of hypergraphs that we call linear hypergraphs, with the aim of creating a sound and complete graphical language for symmetric traced monoidal categories (STMCs). We first define the category of linear hypergraphs as a full subcategory of conventional (simple) hypergraphs, in which each vertex is either the source or the target of exactly one edge. The morphisms of a freely ge...  $\bigtriangledown$  More

Submitted 21 October, 2020; v1 submitted 13 October, 2020; originally announced October 2020. Comments: updated notation and appendices, technical report, 56 pages

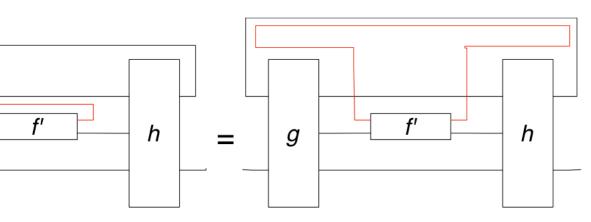

#### Bonus: equations can be expressed as a graph rewriting system

**Corollary 65.** *LHyp* $_{\Sigma}$  *is a partial adhesive category.*